Xilinx Vertex 5 FPGA

This project is completed in Fall 2011 for the UC Berkeley EECS150 class. It is a digital design project implementing a three pipelined stages MIPS instruction set (normally 5 pipelines) onto the Xilinx Vertex 5 Reprogrammable FPGA using Verilog.

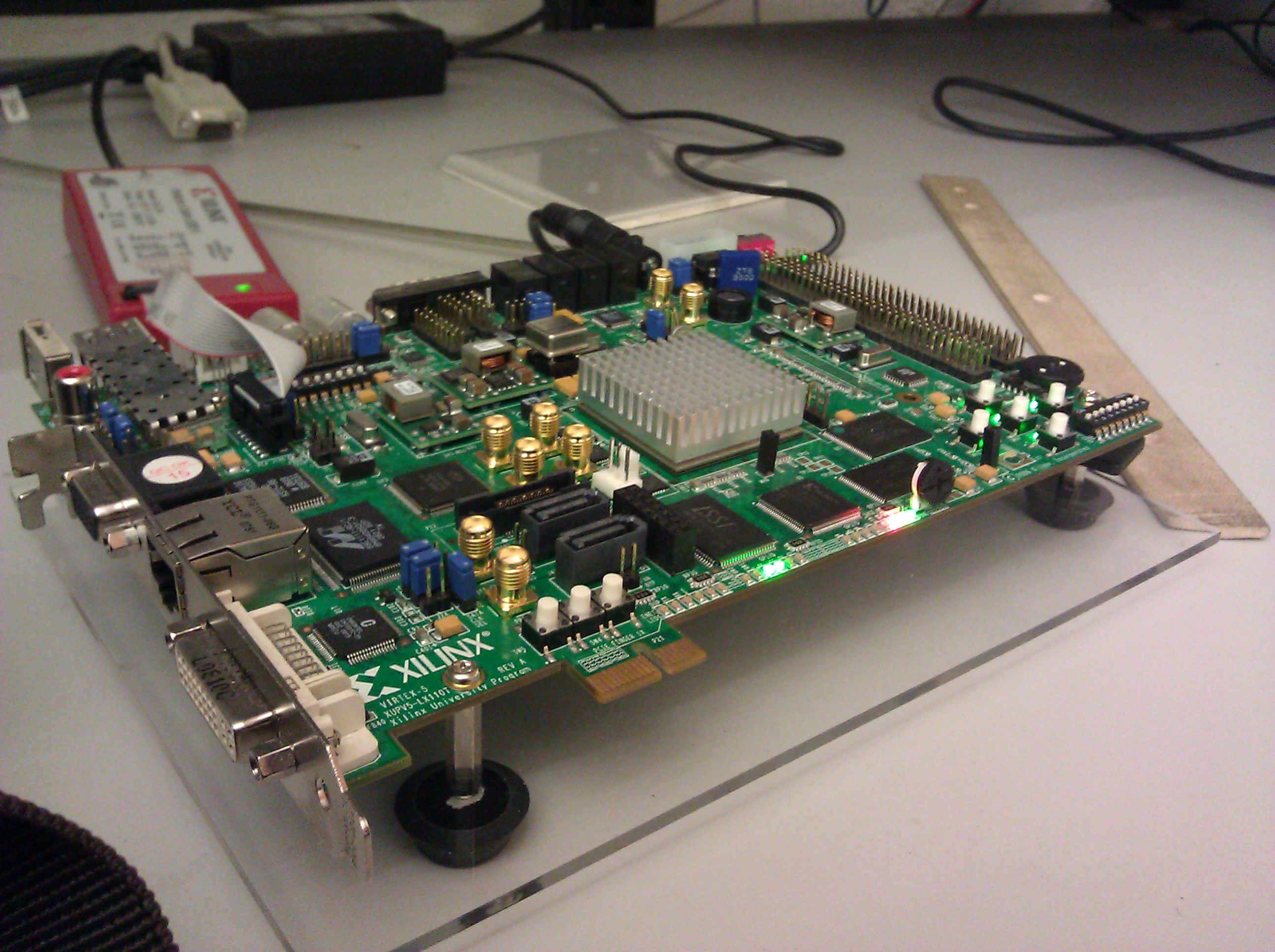

Figure 1. One of the FPGA inside the Berkeley EECS Cory lab.

Figure 1. One of the FPGA inside the Berkeley EECS Cory lab.

This was a semester long project. We have the build everything from scratch, from the RAM and the ROM for memories to the ALU for the execute stage.

The challenge of this project is not the design but the debugging process. Unlike normal sequential programming, we cannot just click the compile button and let the compiler find the error. Coding for hardware is very different; it involves very meticulous details and practices to find those bugs.

The report for the final project is below. Take a look!

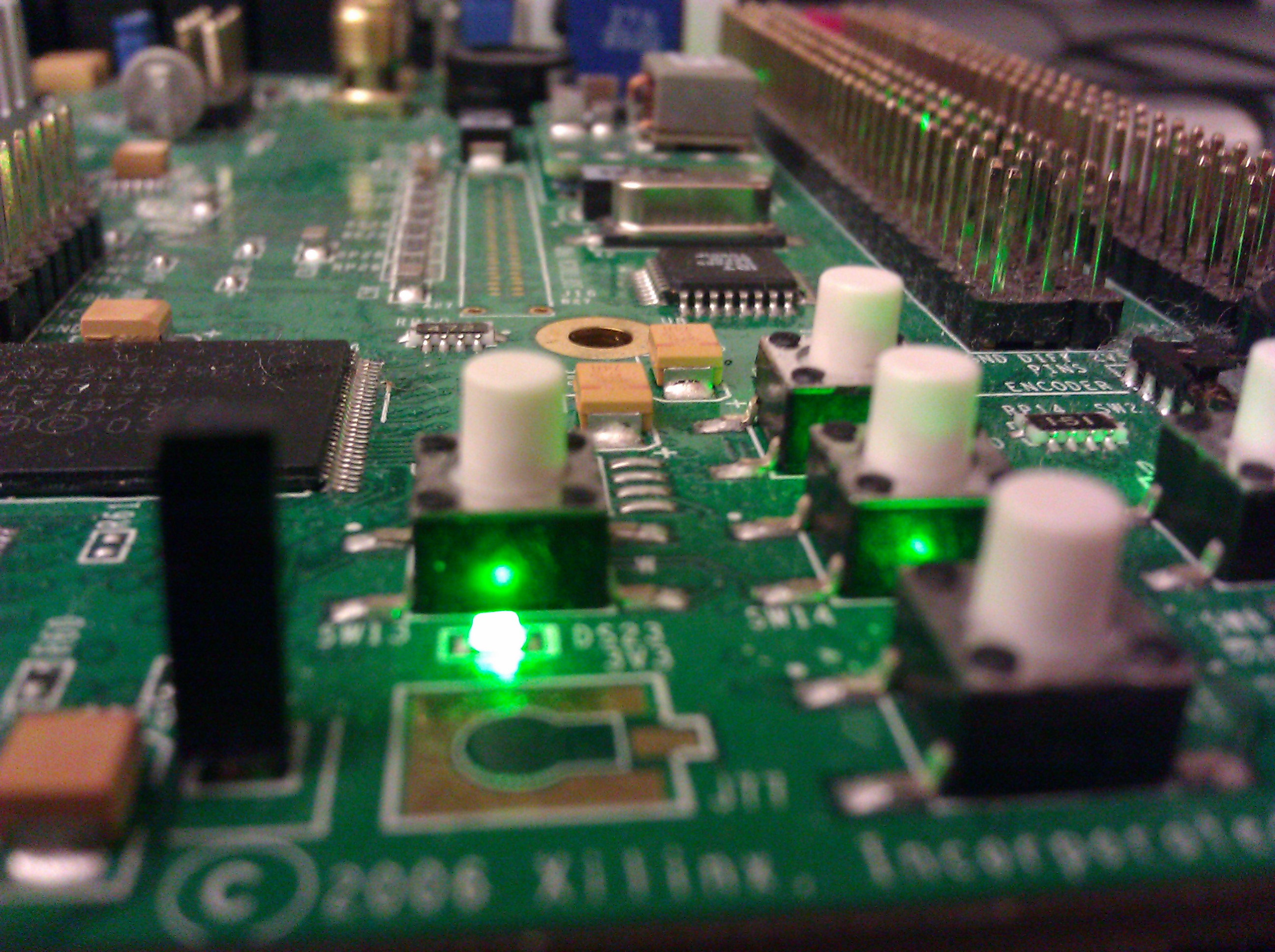

Figure 2. Closeup view of the FPGA.

Figure 2. Closeup view of the FPGA.